- 全部

- 默认排序

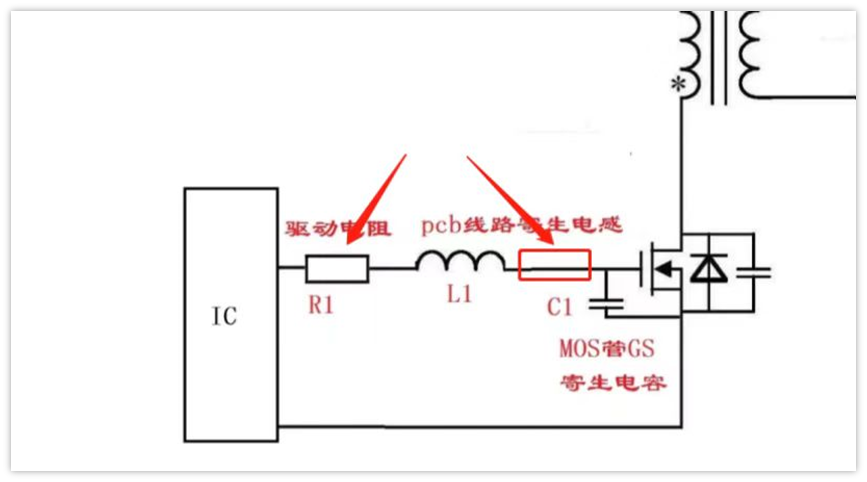

前一段时间有个兄弟问了个问题,把我问住了,问题是这个:如上图,串联的电阻R1到底是放在靠近IC端,还是靠近MOS端?(注意,图中的L1是走线寄生电感,并不是这里放了个电感器件) 我们具体沟通的情况是这样的: 这位兄弟说大部分工程师和IC原厂都是这么做的,但是没有说为什么,我当时也不清楚。但是这个问题

反激式变压器开关电源,是指当变压器的初级线圈正好被直流脉冲电压激励时,变压器的次级线圈没有向负载提供功率输出,而仅在变压器初级线圈的激 励电压被关断后才向负载提供功率输出,这种变压器开关电源称为反激式开关电源。反激开关电源具有高效节能的特点

在高速PCB设计中,过孔(Via)的阻抗计算对于确保信号完整性至关重要。过孔不仅作为导电连接,还承担着信号传输的重要角色。本文将详细介绍过孔阻抗的计算方法和设计注意事项。过孔阻抗的重要性过孔阻抗不匹配会导致信号反射和衰减,影响电路的性能。在

凡亿教育高速PCB线下培训大纲-2025年新版培训工具软件:Altium Designer、Cadence Allegro、Mentor PADS(三款主流EDA软件三选一)开班时间/培训时长:每年三场、每次时长全日制3个月培训,具体开班时

大家好,我是王工。近期在公司PCB layout评审过程中,关于USB3.0背面接口区域是否需要做掏空处理的问题,团队中存在一些不同的见解。今天我想借此机会与大家一起探讨交流这个技术细节,看看大厂都是要求怎么做的。011大厂对高速接口的设计要求在高速信号接口,如USB3.0、HDMI、PCIe、SA

AD19 PCB Layout复制器件,如何复制时,其相应net也随之变化 多组 重复的器件的原理图,画layout时想直接copy 但是每次复制后net 不能相应变化,还需手动更改,求助是否有快捷方式一次性复制到位

我通过region制作了异形焊盘作为IC封装的引脚,在PCB layout中使用该IC时,规则检查时报错short-circuit constraintRegion(0 holes)Top layer Pad U1-(351.132mil, 431.205mil)Top layer

最近硬件工程师同行提出疑问,在硬件设计过程中layout完成后有DRC检查,已经对设计工艺规则做了检查,那么DFM可制造性分析还有必要吗?今天就为大家用一篇文章说明下DRC与DFM两者的区别。可制造性设计 (DFM) 是一种设计验证方法,与

扫码关注

扫码关注